MSc thesis project proposal

[2018] Capacitive sensor-embedded phase locked loop (PLL)

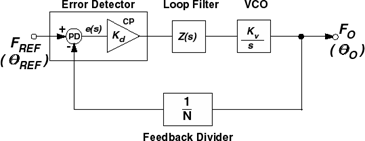

A PLL is a feedback system that combines a VCO with a phase comparator to generate an accurate, stable and variable frequency signal from a fixed low-frequency signal. PLLs are usually employed in transceiver systems to generate accurate mixing frequencies. In the field of biosensing, the frequency-locking feature of PLLs can be exploited to accurately measure the electrical properties of a sensor.

Previous studies have adopted this strategy in combination with resonators, whose electrical properties change as a function of the concentration of biomolecules immobilized on their surface.

In order to avoid the fabrication of costly resonators, an alternative approach would consist of embedding the sensor within the PLL architecture by replacing one of its passive components. For instance, by embedding the sensor within the VCO, the output frequency of the VCO will change as the sensor electrical properties vary. This will force the PLL to initiate a new locking sequence and vary the values of its internal nodes accordingly. The relative change in the value of the probe signals can then be linearly related to the change in the sensor properties and hence to the concentration of the analyte. The embedded-sensor approach would result in a more compact sensor readout architecture with potential for full CMOS integration, hence high-scalability, low cost and multiplexing capabilities.

Assignment

- PLL modeling in Simulink

- PLL modeling in ADIsimPLL

- Sensor design and modeling with capacitance estimation in postlayout simulations

- Discrete implementation of a capacitive sensor PLL

- Schematic and layout design of mixed-signal PLL (phase detector, charge-pump, loop filter, VCO, counter) in Cadence

- Schematic and postlayout simulations of PLL with extracted sensor

Contact

dr. Virgilio Valente

Bioelectronics Group

Department of Microelectronics

Last modified: 2019-12-20